# FE-Analysis of Temperature Distribution of a CMS Silicon Detector Module Using Heat Conduction Cooling via Aluminium Foils

K. Lübelsmeyer, D. Pandoulas,

A. Schultz von Dratzig, R. Siedling

I. Physikalisches Institut RWTH Aachen

and

A. Onnela

CERN/PPE/TA1

#### **Abstract**

A method for cooling the silicon detector modules was investigated in which heat conduction through flexible Al foils glued to the silicon on one end and to a cooling pipe on the other end was taken into account, neglecting a possible convective cooling to the ambient gas. An arrangement for the cooling was found where the overall temperature difference in the silicon wafer is  $\Delta t = 1.3 \mathrm{K}$  at max.

#### 1. Introduction

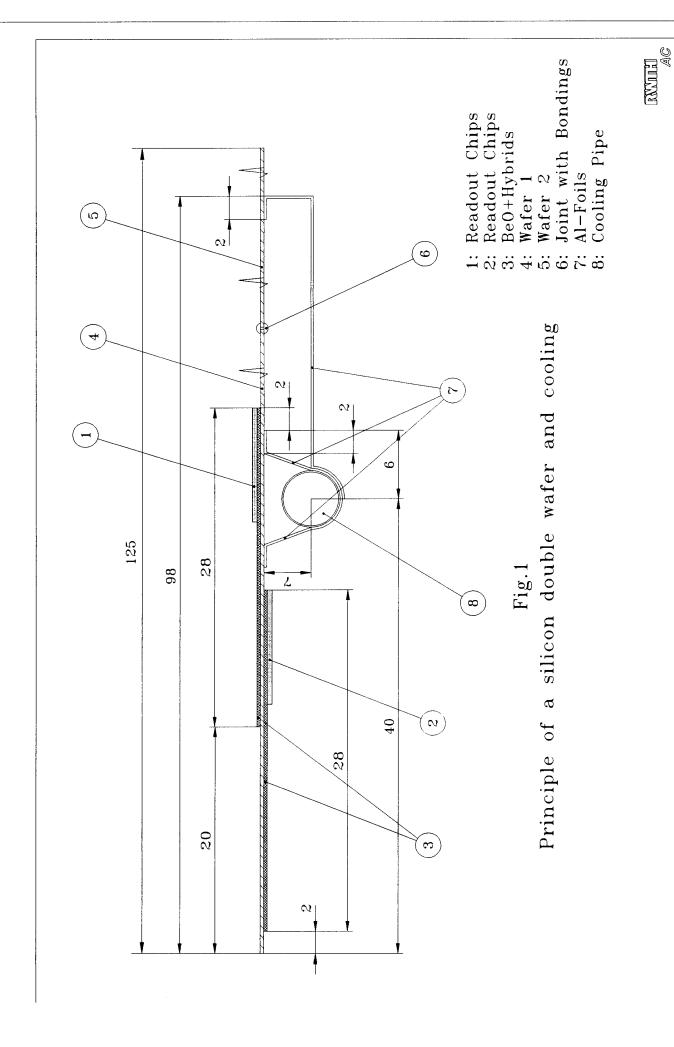

FE-calculations of the temperature distribution of a silicon detector module have been done based on the silicon detector design developed by CERN and the 1<sup>st</sup> Physics Institute of the RWTH Aachen. This design is shown in figure 1. The heat produced by the readout chips and selfheating due to the leakage currents in the silicon wafers is removed by conduction through 3 Al foils glued to the silicon and a cooling pipe thus decoupling the wafers from the possible vibrational motions of the cooling pipe. The Al foils are cut into small parallel strips to have better mechanical flexibility and in order to minimize the bimetallic effect at the junction of Al and Si.

## 2. Dimensions, Temperatures, and Material's Properties

Two silicon wafers, 54 mm wide and 62.5 mm in length each, are glued together and the strips are bonded over the joint. At 2 mm from one end a 0.3 mm thick plate of BeO is glued onto the silicon wafer. It runs over the whole width of 54 mm and has a length of 28 mm. Onto it the 8 readout chips and the rest of the electronical circuitry are mounted. On the other side of the wafer, 2 mm from the end, a similar plate of BeO is glued bearing 2 readout chips for the readout of the stereo strips and the corresponding circuitry. The heat produced by these chips and due to the leakage current in the Si-wafers is removed by conduction through 3 Al foils of 54 mm width glued to the silicon on one end and to the cooling pipe on the other end. The thickness of these Al foils is  $0.2 \, \text{mm}$ , their length 7 mm and 53 mm respectively. The junction areas between Al and silicon are  $2 \times 54 \, \text{mm}^2$  each and between Al and the cooling pipe roughly  $3.3 \times 54 \, \text{mm}^2$ . All layers of glue are supposed to have a thickness of  $0.025 \, \text{mm}$  except for the joint of the two Si-wafers where the thickness of the glue layer is assumed to be  $0.05 \, \text{mm}$ . The two Si-wafers are electrically joined with 1 280 bond wires of Al,  $25 \, \mu \text{m}$  in diameter and  $2.5 \, \text{mm}$  in length each.

The total power of the 10 chips is 2.5 W, the power of the two Si wafers together is 0.4 W. The temperature of the coolant is -3.5 °C. The conduction coefficients are listed in the following table:

| material  | λ<br>W/(mm K)      |

|-----------|--------------------|

| Si        | 0.129              |

| Al        | 0.238              |

| BeO       | 0.180              |

| Glue      | 0.00028            |

| Bond/Glue | 0.000184 + 0.00028 |

The heat transfer coefficient between Al-pipe and the water is supposed to be  $\alpha = 2 \times 10^{-3} \,\mathrm{W/(mm^2 K)}$ .

### 3. Results

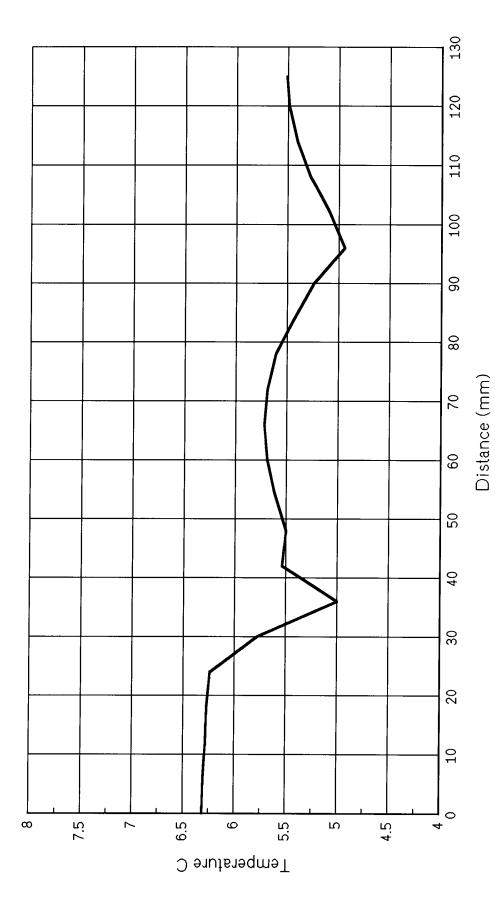

The cooling foils have been shifted along the longitudinal dimension of the Si-wafers until the resulting temperature difference in the Si-wafers was small enough to meet our goal of a  $\Delta t$  of about 1 °C. The positions found to glue the Al foils to the silicon were at 35 mm, 45 mm, and 97 mm measured from the end where the electronics is situated to the middle of the junction areas of the Al foils. The maximum temperature difference with this arrangement has been found to be  $\Delta t = 1.3$  °C. Fig. 2 shows the resulting wafer temperature variation along a line 13.5 mm away from the edge of the Si-wafers corresponding to the position of one of the two stereo readout chips.

Fig. 2: Longitudinal temperature distribution in Si-wafers